電機mos管采樣電阻設計,mos管取樣電阻-KIA MOS管

信息來源:本站 日期:2025-01-23

在電機控制中,采樣電阻通常用于檢測電機相電流。采樣電阻的阻值一般在mΩ到Q之間,具體選擇取決于應用場景和成本考慮。

常用的采樣電阻:高端采樣(Highside sensing)和低端采樣(Low side sensing)。

高端采樣中,采樣電阻位于負載高端,與母線電源連接;低端采樣中,采樣電阻位于負載低端,與地連接。

采樣電阻的位置和電路拓撲結構

低端采樣:這是非常普遍的一種采樣方案,包括三電阻采樣、雙電阻采樣和單電阻采樣。三電阻和雙電阻方案最為常用,適用于成本敏感的應用場景。單電阻采樣方案通過在一個PWM周期內對采樣電阻進行兩次電流采樣來實現。

高端采樣:雖然不常見,但在某些特定應用中也有使用。高端采樣的優點是可以避免低邊MOS開關對采樣的影響,但其實現復雜度較高。

采樣電路的設計步驟和參數選擇

三電阻和雙電阻采樣:在三電阻和雙電阻采樣中,通常在SVPWM的零序矢量處進行采樣,以確保獲得準確的相電流數據。雙電阻方案可以提供更穩定的電流測量,適用于對精度要求較高的場合。

單電阻采樣:通過在一個PWM周期內對采樣電阻進行兩次采樣來實現。這種方法在成本和精度之間做了權衡,適用于成本敏感的應用。

MOS管的選擇

1.場效應管的耐壓:Vin-max+Vor+設定允許的尖峰電壓+留一定的裕量;

2.MOS管的電流,依據變壓器的計算可知其平均電流以及峰值電流;

注意:一般情況下,通過MOS管的電流越大,內阻越小,但是當MOS管溫度升高時會導致內阻增大。同時MOS管有他的一個結溫大小,不能超過,否則會燒壞MOS;

3.Rds-on越小越好,考慮能接受的一個導通損耗來進行選取。

先講述MOS的工作情況及機理,然后說明其周邊器件的作用及如何取值

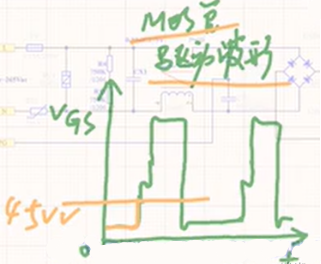

上圖1為MOS管的驅動波形,注意看上升跟下降有抖動,原因是MOS管有寄生電容跟電感,之間發生LC諧振

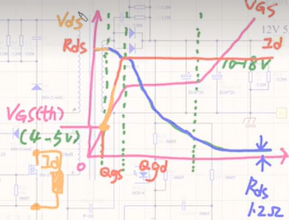

圖2為MOS管VGS之間的電壓以及VDS/Rds的一個波形圖

基于此圖可知,當產生的PWM給MOS的寄生電容Cgs充電,導致VGS電位到該MOS的閾值電壓時(4-5V)此時MOS管開始導通,MOS可等效為一個電阻可調的。

由于一開始MOS的D極接整流后的電壓,電壓會給MOS的寄生電容Cgd充電,電容產生左負右正的電動勢,當MOS管達到閾值電壓,開始導通時,電容Cgd通過MOS管放電,因而會分流PWM給MOS的寄生電容Cgs充電,因而產生一個米勒平臺(圖2中水平線,圖1第一個上升的抖動時間,到第二個上升為止)又在米勒平臺剛形成的時候,Id就已經達到最大值了,故而米勒平臺將會產生開關損耗,這個持續的時間由這個米勒電容Cgd的大小決定。當米勒電容Cgd放電完成且PWM給他反向充電,充滿以后,(米勒平臺消失)PWM接著給Cgs充電,使得Vgs的電位接著抬高,以及達到Rds的阻值很小的狀態。

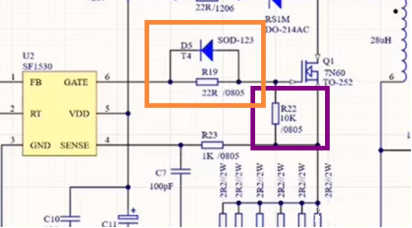

圖3中紫色框的區域,與MOS并聯的電阻R22為下拉電阻,作用,若無這個下拉電阻由于MOS的寄生電容Cgs的存在,擾動或是些干擾,可能導致MOS管誤導通。因而此下拉電阻的作用是給寄生電容Cgs提供一個放電回路,保證MOS的低電平可靠;

圖中黃色框的區域,R19是阻尼電阻,若取大,可能會導致給到MOS,G極的電壓不夠,驅動不了MOS管開通,若取小了,會導致給到寄生電容Cgs過多能量,等MOS關斷時,將通過走D5放掉這部分能量,造成不必要的功耗。

聯系方式:鄒先生

座機:0755-83888366-8022

手機:18123972950(微信同號)

QQ:2880195519

聯系地址:深圳市龍華區英泰科匯廣場2棟1902

搜索微信公眾號:“KIA半導體”或掃碼關注官方微信公眾號

關注官方微信公眾號:提供 MOS管 技術支持

免責聲明:網站部分圖文來源其它出處,如有侵權請聯系刪除。