靜態功耗詳解,降低靜態功耗的方法-KIA MOS管

信息來源:本站 日期:2024-01-12

功耗

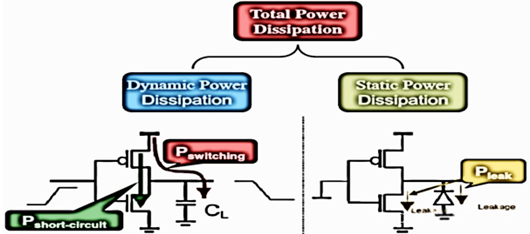

功耗 = 靜態功耗 + 動態功耗

= 靜態功耗 + 轉換功耗 + 短路功耗

功耗源

功耗的本質是能量耗散。由能量守恒定律可知,能量只能從一種形式轉成另一種形式,能量的總量不變。芯片耗散的電能主要轉化成熱能。如果一顆芯片的功耗過大,容易導致工作時溫度過高,造成功能失效,甚至晶體管失效。因此,減小芯片功耗是很重要的一個任務。靜態功耗以及動態功耗是兩個主要的功耗源。

靜態功耗

P_static=V*I_leak,和電壓、漏電流有關,而漏電流和工藝有關;

電壓角度V:

(1)降低工作電壓;

(2)多電壓域;

(3)動態電壓縮放DVS技術(處理器在不同工作模式下使用不同電壓);

(4)電源關斷技術,power-gating;

電流角度I_leak(漏電流):

(1)使用HVT高閾值晶體管,漏電流小;

(2)多閾值;

靜態功耗

靜態功耗主要來源于:

(1)流過截止晶體管的亞閾值泄漏電流(subthresholdleakage)

(2)流過柵介質的泄漏電流(gateleakage)

(3)源漏擴散區的p-n節泄漏電流(junctionleakage)

(4)在有比電路中的競爭電流

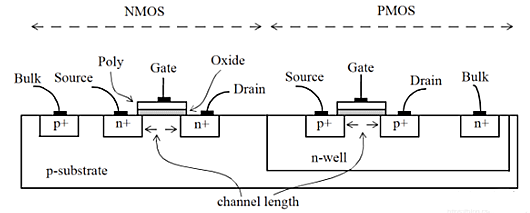

2.1亞閾值泄漏電流

亞閾值泄漏電流是晶體管應當截止時流過的電流。在90nm節點之前,泄漏功耗主要在休眠模式下才考慮,這是因為它與動態功耗相比可以忽略不計。但是在低閾值電壓和薄柵氧的納米工藝中,泄漏電流占到總工作功耗的1/3。

亞閾值泄漏電流與多種因素有關。提高源極電壓或應用一個負的體電壓可以減小泄漏。泄漏電流還與溫度有關,限制芯片溫度對于控制泄漏至關重要。另外,通過兩個或更多個串聯晶體管的泄漏電流會應堆疊效應(stackeffect)而大大減小。例如兩輸入與非門,兩個NMOS堆疊在一起。

2.2柵泄漏電流

柵極泄漏電流發生在一個電壓加到柵上時(例如當門導通時)載流子遂穿通過薄柵介質的情況下。泄漏電流與介質厚度有極強的關系。工藝中通過選擇合適厚度的介質將柵泄漏電流限制到一個可接受的水平上。泄漏電流還取決于柵極電壓。通過使晶體管堆疊起來并使截止晶體管靠近電源/地線可以使柵泄漏電流減小。

2.3結泄漏電流

結泄漏電流發生在源或漏擴散區處在與襯底不同電位的情況下。結泄漏電流與其他泄漏電流相比時通常都很小。

2.4競爭電流

靜態CMOS電路沒有任何競爭電流,但其他某些電路甚至在靜態時本身就會吸取電流。電流模式邏輯和許多模擬電路也會吸取靜態電流。這樣的電路應該在休眠模式時通過禁止上拉或電流源工作來關斷他們。

2.5降低靜態功耗辦法

(1)電源門控減小靜態電流最容易的方法就是關斷休眠模塊的電源。這一技術稱為電源門控。

(2)多種閾值電壓和柵氧厚度有選擇的應用多種閾值電壓可以使具有低Vt晶體管保持性能而又使具有高Vt晶體管的其他路徑減少泄漏。大多數納米工藝的邏輯管采用薄柵氧,IO晶體管采用厚的多的柵氧以使它們能夠承受較大的電壓。

(3)可變閾值電壓通過體效應可以調制閾值電壓。在休眠模式下應用一個反向體偏置減小泄漏。在工作模式下利用一個正向體偏置來提高性能。

(4)輸入向量控制由前面可知,堆疊效應和輸入排序會引起亞閾值泄漏和柵泄漏的變化。因此,一個邏輯模塊的泄漏與門的輸入有關。輸入向量控制是當模塊置于休眠模式時,應用一組輸入圖案使模塊的泄漏最小。這些輸入向量可以通過寄存器上的置位/復位輸入端或通過掃描鏈加入。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950(微信同號)

QQ:2880195519

聯系地址:深圳市福田區金田路3037號金中環國際商務大廈2109

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關注”官方微信公眾號

請“關注”官方微信公眾號:提供 MOS管 技術幫助

免責聲明:本網站部分文章或圖片來源其它出處,如有侵權,請聯系刪除。