MOSFET-襯底偏壓技術圖文詳解-KIA MOS管

信息來源:本站 日期:2023-06-19

先簡單回顧下MOSFET的導通過程。

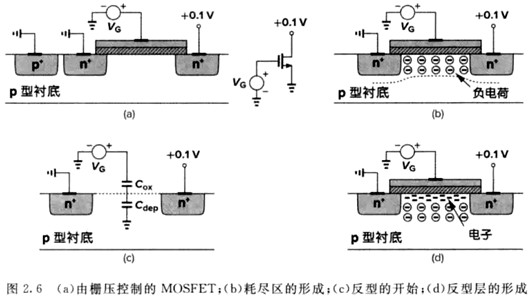

當Vg從0V開始上升的時候,p襯底中的多子空穴會被趕離柵區從而留下負電荷(空穴無法移動,實際上是電子的移動,電子從襯底被抽取上來,與p型半導體中的受主雜質例如硼結合,使得共價鍵飽和,既沒有可移動的電子,也沒有可移動的空穴);

此時柵極與襯底構成電容器的兩極,因此襯底上負電荷的量和柵上正電荷的量相同; 由于p型半導體中是多子空穴導電,最終在p型襯底中形成一個多子耗盡的區域即耗盡層;

隨著Vg增加,耗盡層寬度以及,氧化物和硅界面處的電勢也增加; 這時結構類似兩個電容串聯:柵氧化層電容(Cox,這是一個固定電容,Cox = εox/dox)和耗盡層電容(Cdep,這是一個可變電容,Cdep = εdep/ddep,ddep耗盡層寬度會增加);

當Vg進一步增加的時候,源漏之間的柵氧下就形成了載流子溝道; 形成溝道所對應的Vg成為閾值電壓Vth;

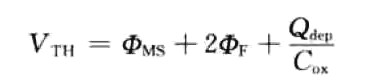

Vth通常定義為界面的電子濃度等于p型襯底的多子濃度時的柵壓; Vth有如下表達式:

其中Qdep是耗盡層的電荷;

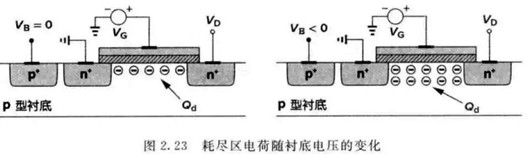

以上討論都是假設襯底和源端是接地的,如果NMOS的襯底電壓Vb比源端電壓Vg小的時候會發生什么情況。

假設Vs=Vd=0,Vg略小于Vth使得柵下形成耗盡層但是還沒有反型層形成。 當Vb變得更負的時候,將會有更多的空穴被吸引到襯底,同時留下大量的負電荷,耗盡層變得更寬了,由Vth的表達式可知,閾值電壓是耗盡層電荷總數的函數,因為在反型之前,柵上的電荷是等于耗盡層電荷的。

因此,隨著Vb的下降,Qd增加,Vth也增加。 這稱為反向襯底偏置或者體效應,可以表達為如下公式:

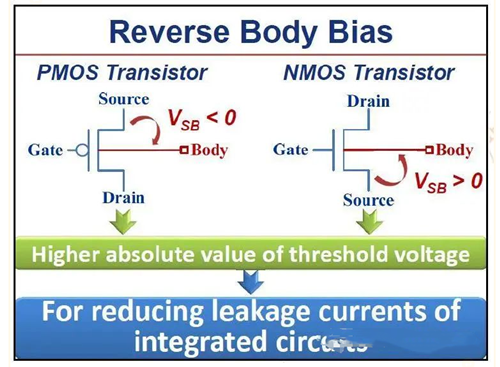

而閾值電壓的增大,可以降低晶體管的漏電流,這種低功耗技術就稱為反向襯底偏置技術。

上述討論同時適用于PMOS,區別在于,對于PMOS來說,襯底加正偏壓,Vsb < 0時閾值電壓會增大。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區金田路3037號金中環國際商務大廈2109

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關注”官方微信公眾號

請“關注”官方微信公眾號:提供 MOS管 技術幫助

免責聲明:本網站部分文章或圖片來源其它出處,如有侵權,請聯系刪除。