ESD防護設計-常見ESD保護電路圖-KIA MOS管

信息來源:本站 日期:2023-05-30

ESD防護設計

ESD防護設計的目的是,當集成電路任意兩個輸入/輸出引腳之間發生ESD事件時,集成電路內部的ESD防護系統能及時開啟來泄放掉大量的瞬時電流/電壓,使內部電路免遭破壞。此外,在集成電路正常工作時,即未發生ESD事件時,ESD系統引入的寄生參數不會影響電路的正常工作。

具體要求為:

1、當ESD 沖擊出現時,ESD保護器件能夠快速開啟,高效泄放沖擊大電流,鉗位到安全電壓。

2、在ESD 沖擊下具有一定程度的魯棒性,確保ESD保護電路自身能夠承受外“部沖擊。

3、當IC處于正常工作狀態時,ESD保護器件處于關閉狀態,不影響電路正常功能。

4、ESD保護電路一般在IO pad的周圍,需保證較小的IO延遲.

5、占用較小的芯片面積,提供較高的ESD保護能力。

6、保持較高抗門鎖能力。

7、盡量在不增加額外步驟或掩膜的情況下制造ESD保護電路。

ESD防護電路設計

ESD保護電路中器件的使用

在集成電路設計中加入ESD保護電路,當ESD來的時候,ESD保護電路發揮保護效果,避免集成電路內的元件被ESD損傷。

當ESD電壓出現在芯片PIN腳上時,位于該PIN腳附近的ESD保護電路必須及早地導通來泄放ESD電流。因此,ESD保護電路所使用的元件必須要具有較高的擊穿電壓或較快的導通速度,同時也需要注意在芯片正常工作時ESD保護電路不能影響芯片功能。

電阻(Diffusion or poly resistor)、二極管(P-N junction)、金屬-氧化物-半導體晶體管(NMOS or PMOS)、厚氧化層元件(Field-oxide device)、寄生的雙極型晶體管(BJT)、寄生的可控硅元件(SCR device)、這類器件可以組合使用可單獨使用。

ESD防護電路

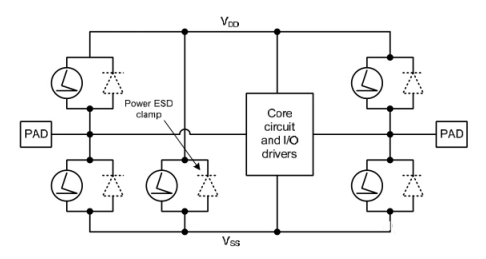

基于可能發生的ESD事件分析,ESD可能會發生在I/O、PIN與電源和地之間,也會發生在不同的I/O PIN之間,也可能出現在電源和地之間,因此對于ESD保護電路的設計需要考慮所有可能發生ESD的情形。

ESD防護電路

常見的ESD保護電路設計

目前現有的ESD保護電路及其功能模塊的設計。

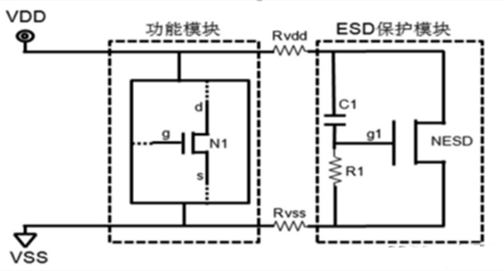

ESD防護電路的功能模塊和保護模塊

在全芯片的ESD結構設計時,需注意以下原則:

(1)外圍VDD、VSS走線盡可能寬,減小走線上的電阻;

(2)設計一種 VDD-VSS之間的電壓箝位結構,且在發生ESD時能提供VDD-VSS直接低阻抗電流泄放通道。對于面積較大的電路,在芯片的四周各放置一個這樣的結構,若有可能,在芯片外圍放置多個VDD、VSS的PAD,也可以增強整體電路的抗ESD能力;

(3)外圍保護結構的電源及地的走線盡量與內部走線分開,外圍ESD保護結構盡量做到均勻設計,避免版圖設計上出現ESD薄弱環節;

(4)ESD保護結構的設計要在電路的ESD性能、芯片面積、保護結構對電路特性的影響如輸入信號完整性、電路速度、輸出驅動能力等進行平衡考慮設計,還需要考慮工藝的容差,使電路設計達到化;

(5)在實際設計的一些電路中,有時沒有直接的VDD-VSS電壓箝位保護結構,此時,VDD-VSS之間的電壓箝位及ESD電流泄放主要利用全芯片整個電路的阱與襯底的接觸空間。所以在外圍電路要盡可能多地增加阱與襯底的接觸,且N+P+的間距一致。若有空間,則在VDD、VSS的PAD旁邊及四周增加VDD-VSS電壓箝位保護結構,這樣不僅增強了VDD-VSS模式下的抗ESD能力,也增強了I/O-I/O模式下的抗ESD能力。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區金田路3037號金中環國際商務大廈2109

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關注”官方微信公眾號

請“關注”官方微信公眾號:提供 MOS管 技術幫助

免責聲明:本網站部分文章或圖片來源其它出處,如有侵權,請聯系刪除。