低功耗設計—功耗構成和類型圖文分享-KIA MOS管

信息來源:本站 日期:2022-04-19

低功耗按照類型分類,其構成主要有動態功耗、靜態功耗、浪涌功耗這三種。

1)動態功耗

動態功耗包括:開關功耗或者稱為翻轉功耗、短路功耗或者稱為內部功耗。

①開關功耗

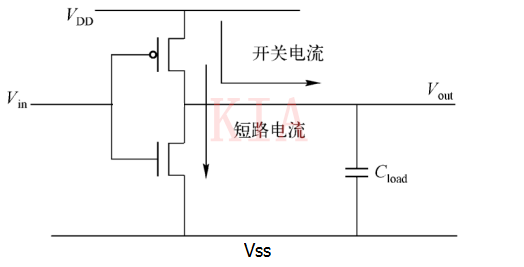

在數字CMOS電路中,對負載電容進行充放電時消耗的功耗,比如對于下面的CMOS非門中

當Vin = 0時,上面的PMOS導通,下面的NMOS截止;VDD對負載電容Cload進行充電,充電完成后,Vout的電平為高電平。

當Vin = 1時,上面的PMOS截止,下面的NMOS導通,負載電容通過NMOS進行放電,放電完成后,Vout的電平為低電平。

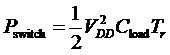

這樣一開一閉的變化,電源的充放電,就形成了開關功耗,開關功耗Psitch的計算公式如下所示:

在上式中,VDD為供電電壓,Cload為后級電路等效的電容負載大小,Tr為輸入信號的翻轉率。一般情況下,信號在一個周期內平均翻轉兩次,即上升沿一次、下降沿一次,也就是說,Tr = 2f,因此,平均功耗就是:

Pdynamic = Vdd*Vdd*CL*f

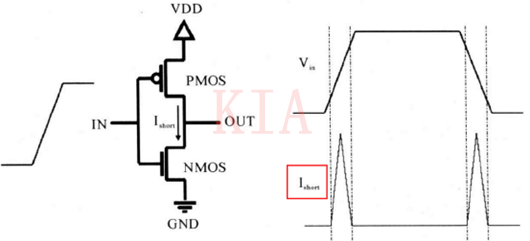

②短路功耗

短路功耗也稱為內部功耗,短路功耗是因為在輸入信號進行翻轉時,信號的翻轉不可能瞬時完成,因此PMOS和NMOS不可能總是一個截止另外一個導通,總有那么一段時間是使PMOS和NMOS同時導通,那么從電源VDD到地VSS之間就有了通路,就形成了短路電流,如下面的反相器電路圖所示:

短路功耗Pshort的計算公式如下所示:

上式中,Vdd為供電電壓,Tr為翻轉率,Qx為一次翻轉過程中從電源流到地的電荷量。

由此我們可以找到,動態功耗主要有開關功耗和短路功耗;其中開關功耗在動態功耗中占大部分比例;從上面的兩個式子中我們可以看到,動態功耗主要跟電源的供電電壓、翻轉率、負載電容有關。

2)靜態功耗

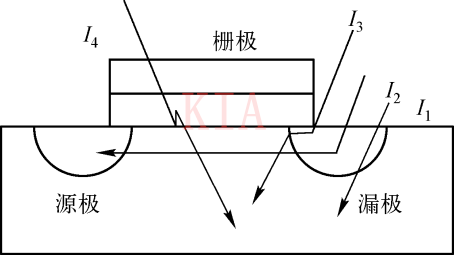

在CMOS電路中,靜態功耗主要是漏電流引起的功耗,如下圖所示:

漏電流有下面幾個部分組成:

·PN結反向電流I1(PN-junction Reverse Current)

·源極和漏極之間的亞閾值漏電流I2(Sub-threshold Current)

·柵極漏電流,包括柵極和漏極之間的感應漏電流I3(Gate Induced Drain Leakage)

·柵極和襯底之間的隧道漏電流I4(Gate Tunneling)

一般情況下,漏電流主要是指柵極泄漏電流和亞閾值電流(進入超深亞微米工藝之后,隧道漏電流成為主要電流之一),因此下面就簡單介紹一下這兩種電流。

柵極泄漏功耗:在柵極上加信號后(即柵壓),從柵到襯底之間存在電容,因此在柵襯之間就會存在有電流,由此就會存在功耗。

亞閾值電流:使柵極電壓低于導通閾值,仍會產生從FET漏極到源極的泄漏電流。此電流稱為亞閾值泄漏電流。在較狹窄的晶體管中,漏極和源極距離較近的情況下會產生亞閾值泄漏電流。晶體管越窄,泄漏電流越大。要降低亞閾值電流,可以使用高閾值的器件,還可以通過襯底偏置進行增加閾值電壓,這些屬于低功耗設計。

靜態功耗的計算公式如下所示,Ileak為泄漏電流(Ipeak應該是Ileak):

靜態功耗往往與工藝有關。

(3)浪涌功耗

浪涌功耗是浪涌電流引起的功耗。浪涌電流是指開機或者喚醒的時候,器件流過的最大電流,因此浪涌電流也稱為啟動電流。一般情況下,浪涌功耗不是我們關注的地方,因此這里只是說明有這個功耗存在。

功耗的構成——按結構分

前面按照類型進行功耗分類,這里使用結構進行分類,也就是根據設備的結構或者設備的構成進行分類。

(以SoC為例)主要分為:時鐘樹功耗、處理器功耗、存儲器功耗、其他邏輯和IP核功耗、輸入輸出pad功耗。在不同的應用、設備中,這些功耗的比例不一樣,但是時鐘樹、處理器、存儲器占了絕大部分功耗,這是需要說明的。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區車公廟天安數碼城天吉大廈CD座5C1

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關注”官方微信公眾號

請“關注”官方微信公眾號:提供 MOS管 技術幫助

免責聲明:本網站部分文章或圖片來源其它出處,如有侵權,請聯系刪除。