CMOS集成電路的自我隔離-KIA MOS管

信息來源:本站 日期:2021-07-19

無論是雙極性集成電路,到現在主流的CMOS集成電路,基本都是靠PN結隔離。

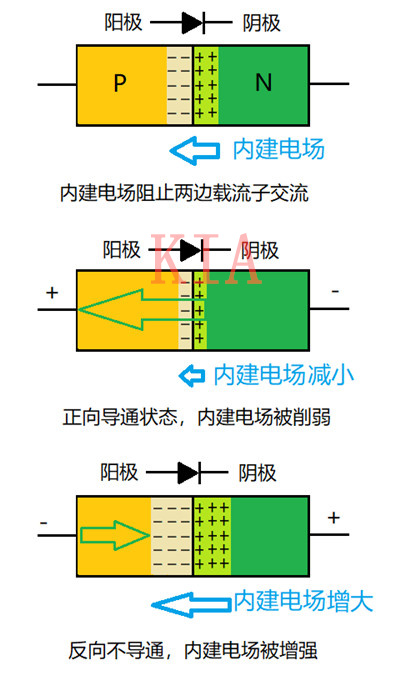

我們知道,PN結之所以叫“結”,就是在結合處會成一個內建電場,這個內建電場阻止了P型(空穴多)和N型(電子多)載流子的進一步復合。所以PN結加正向電壓,內建電場被削弱,PN結導通。

加反向電壓,增強了內建電場,PN結不導通。利用PN結的反偏不導通可以做到晶體管之間的隔離效果。為了便于對照,我們把PN結的狀態(零偏正偏反偏)示意圖如下。

反向PN結可以用作隔離

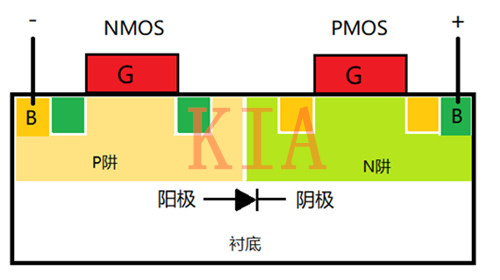

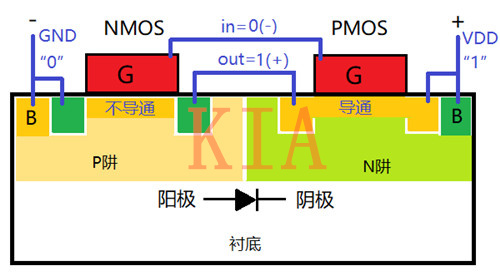

下面是CMOS集成電路的基本單元示意圖:NMOS管和PMOS管。

它們的不同搭配組合可以形成許許多多的邏輯電路。圖中綠色代表N型區,黃色代表P型區,不同顏色深淺代表濃度不同。

NMOS位于P阱內,PMOS位于N阱內,P阱和N阱就構成了一個PN結,阱的引出端是各自的B端。

要讓PMOS管和NMOS管互相隔離,就得采用反偏電壓。所以一定是P阱接低電平,N阱接高電平。普通邏輯或數字電路無一例外。

很多工藝為了簡單,可以只做一個阱,把襯底當作另外一個阱。如果是N型襯底,那就相當于圖中N阱擴展到了下面,襯底得接高電平。如果是P型襯底,那就相當于圖中P阱擴展到了下面,襯底得接低電平。

理解了CMOS器件的隔離技術,就很容易看懂版圖:接VDD高電平的都是PMOS,位于N阱內。接GND低電平的都是NMOS,位于P阱內。

另外由于NMOS是電子導電,PMOS是空穴導電。電子的遷移率比空穴大,所以為了平衡,相同性能的P管寬長比一般比N管大一些。這樣更容易從電源的接法和晶體管的大小就很容易識別PMOS和NMOS版圖。

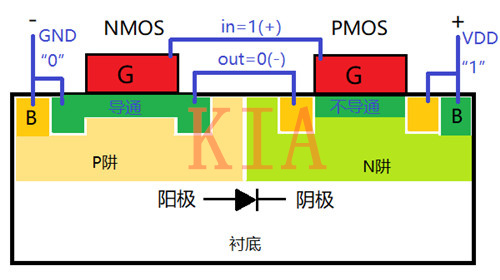

有人說,這樣接法的限制會不會影響電路設計呢?我們來看一個簡單的例子。

如下圖所示,將阱偏置好的PMOS及NMOS用藍線連接,則可以得到:當in端為高電平“1”時,就會在兩個管子溝道處感應出電子來,導致NMOS導通,PMOS不導通。out端就變成了低電平“0”。

CMOS倒相器工作原理1

相反,如下圖所示,當in端為低電平“0”時,就會在兩個管子溝道處感應出空穴來,導致PMOS導通,NMOS不導通。out端就變成了高電平“1”。

CMOS倒相器工作原理2

除了倒相器,CMOS在阱固定反向偏置下,還可以形成與非門、或非門等等邏輯電路。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區車公廟天安數碼城天吉大廈CD座5C1

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關注”官方微信公眾號

請“關注”官方微信公眾號:提供 MOS管 技術幫助